The Second Wave of HLS: Why Iteration Speed Now Matters More Than Abstraction

High-Level Synthesis has already passed its most important test. The industry now knows that higher abstraction can generate real hardware. Many companies have successfully deployed HLS in production silicon, and in certain domains—such as AI accelerators, networking pipelines, and video processing—the methodology has demonstrated clear productivity advantages. The debate over whether HLS works is largely over. The more interesting question is what comes next. Because the pressures shaping modern silicon programs are changing what engineering teams need from abstraction.

The first wave proved the concept

The first generation of HLS tools focused on demonstrating a fundamental capability: that algorithmic descriptions could be translated into synthesizable hardware. That achievement mattered enormously. It validated the idea that engineers could design functionality at a higher level while still producing competitive RTL implementations. For many teams, the first successful HLS deployment delivered immediate benefits. Certain blocks moved faster from concept to implementation. Algorithm developers could contribute more directly to hardware development. Some architectural experiments became easier to express. But those early successes also revealed a new reality. Once abstraction works, the real question becomes how well it scales.

Where the next bottleneck appears

As HLS adoption expanded, engineering teams began to encounter a different set of challenges. Iteration loops sometimes remained longer than expected. QoR could diverge between the HLS environment and downstream synthesis. Design tuning still required specialized expertise. And in many organizations, HLS remained confined to a relatively small group of specialists. None of these issues invalidates the value of abstraction. But they do reveal a deeper truth about modern silicon programs. The limiting factor in many design flows is no longer the ability to express functionality. It is the speed at which teams can evaluate architectural decisions.

The economics of iteration

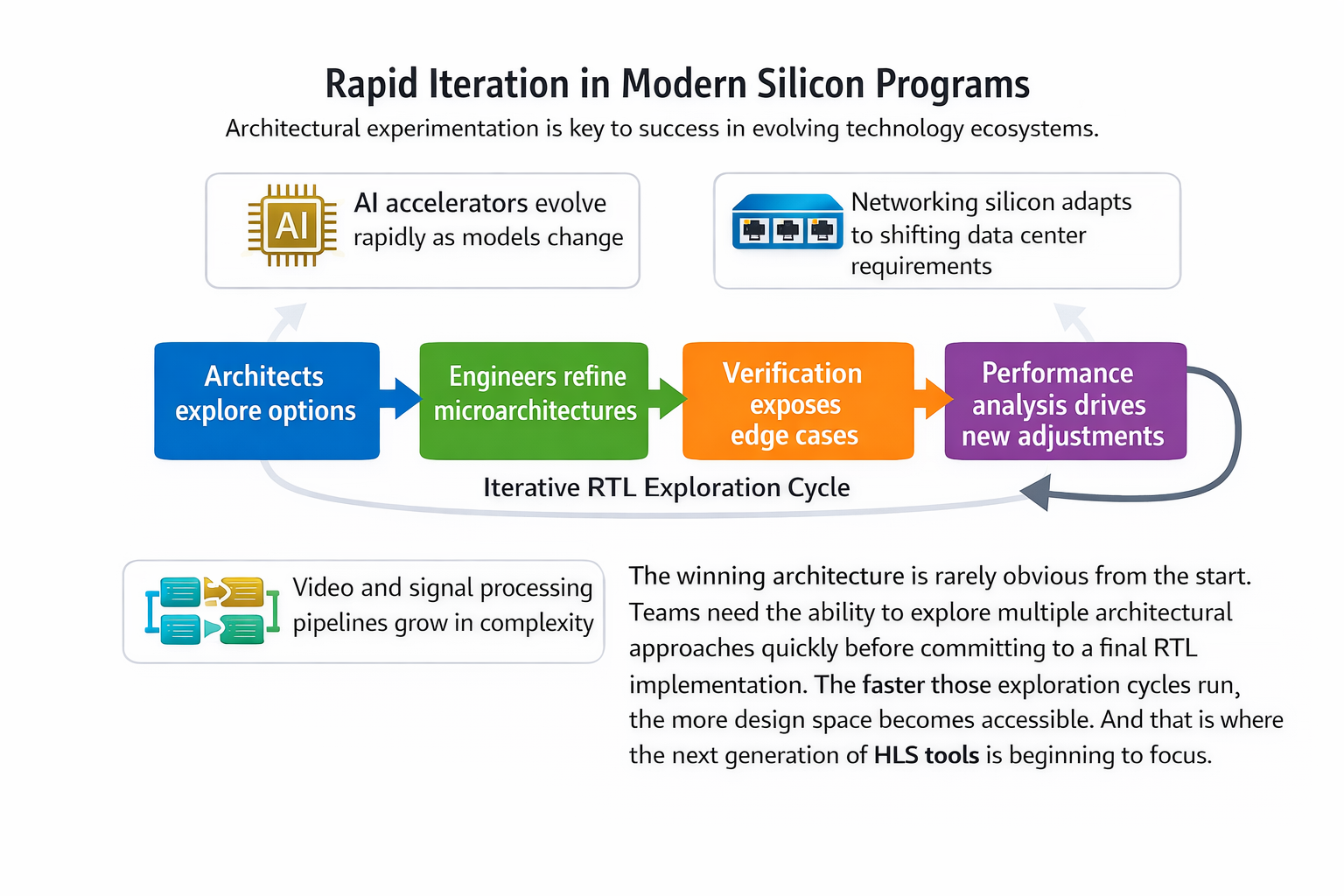

Chip design has always involved iteration. Architects explore options. Engineers refine microarchitectures. Verification exposes edge cases. Performance analysis drives new adjustments.

But as silicon complexity increases, the cost of each iteration loop becomes more significant. Every additional loop consumes engineering time, compute resources, and schedule margin. When iteration cycles stretch too long, architectural exploration narrows, and teams may converge prematurely on suboptimal designs. In that environment, the most valuable design tools are not necessarily the ones with the most features. They are the ones that allow engineers to reach the right architectural decision faster.

The emergence of second-generation HLS

This shift in priorities is shaping the next phase of HLS evolution. The goal is no longer simply to raise the level of abstraction. That problem has largely been solved. The new objective is to optimize the economics of hardware design iterations. Second-generation HLS approaches focus on:

• Faster compile and synthesis cycles

• Stronger correlation with downstream implementation tools

• Reduced reliance on specialized tuning expertise

• Workflows that allow RTL engineers to participate directly in higher-level design

In other words, the emphasis is shifting from abstraction itself to the speed and reliability of architectural exploration.

Why this matters now

Modern silicon programs are increasingly defined by architectural experimentation. AI accelerators evolve rapidly as models change. Networking silicon adapts to shifting data center requirements. Video and signal processing pipelines continue to grow in complexity. In these environments, the winning architecture is rarely obvious from the start. Teams need the ability to explore multiple architectural approaches quickly before committing to a final RTL implementation. The faster those exploration cycles run, the more design space becomes accessible. And that is where the next generation of HLS tools is beginning to focus.

Where Rise fits

Rise Design Automation reflects this shift toward iteration-driven design. The company’s approach emphasizes faster design-space exploration, improved synthesis correlation, and workflows that integrate naturally with SystemVerilog-based design environments.

Rather than positioning HLS as a replacement for traditional RTL engineering, this approach treats higher abstraction as a tool for accelerating architectural decision-making. For many teams, that distinction is important. The goal is not to abandon established RTL flows. It is to reach the right RTL architecture sooner.

The Watchtower signal

The industry conversation around HLS is evolving. The first wave asked: “Can abstraction generate real hardware?” The second wave is asking something different: “How quickly can we reach the right architecture?”

The Watchtower view

The future of hardware design will not be defined solely by abstraction levels. It will be defined by how quickly engineering teams can explore architectural possibilities and converge on the best implementation. HLS opened the door to higher abstraction.

The next generation of tools will determine whether that abstraction truly scales across the complexity of modern silicon programs. And in the coming years, the tools that win may not simply be the ones that generate hardware.

They will be the ones that allow engineers to discover the right hardware faster.

For more insights like this go to: AI TechSales Blog AKA The Watchtower Brief